What is a timing violation

Mia Kelly

Published Mar 17, 2026

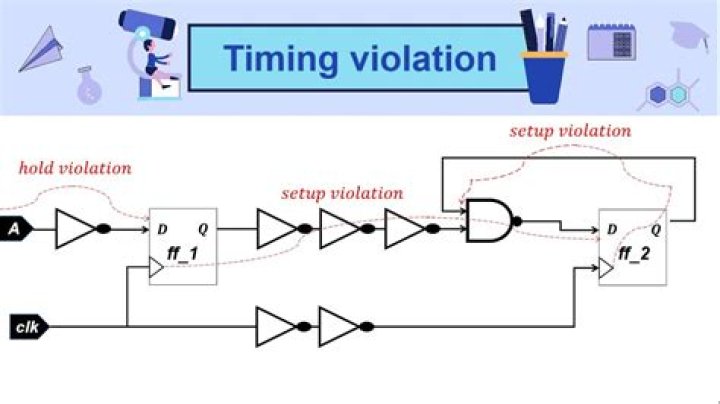

Timing violations occur when the execution time requested by sections of code is shorter than execution time the bitfile achieves after compiling.

How do I fix my time violation?

- Use larger/stronger cells to drive paths with high capacitance, which can reduce the time needed to transition on sluggish net.

- Adjust the skew of the clock to the start or endpoint of the path which is violating.

What happens when setup time is violated?

Setup time is defined as the minimum amount of time before the clock’s active edge that the data must be stable for it to be latched correctly. … Violation in this case may cause incorrect data to be latched, which is known as a hold violation.

What causes hold time violations?

Hold time is defined as the minimum amount of time AFTER the clock’s active edge during which the data must be stable. Any violation in this required time causes incorrect data to be latched and is known as a hold violation. For more information on the intra-flop aspects of setup and hold time, see Reference 1.What is timing violations in VLSI?

If m < H , it results into timing violation, called as Hold violation. This means, that the combinational logic delay is very less and hence data change is very fast. … This means, that the combinational logic delay is very large and hence data change is very slow.

Which is hard to fix setup violation or hold violation and why?

Short answer: Setup violation depends on the data path delay while hold violation depends on the clock path delay. Before CTS, clock path is taken as ideal because we don’t have skew and transition numbers of the clock path, but this information is sufficient to perform Setup Analysis .

What will happen if there is setup time and hold time violation How do you overcome this?

While the hold time violation can be solved by inserting delay between the launching and capturing FF, nevertheless, one shall be careful that this does not create a new critical path. On the other hand, setup time violations can be solved by increasing the clock period.

How do I check my hold time violation?

In a hold-time test, the observation point must be initialized with a value that coin- cides with the correct value. If there is shoot-through of the value in the flip-flop previous to the launch flip-flop, then the test will fail.What happens if there is hold violation?

As a result of that there occurs a Hold violation. This type of violation (Hold Violation) can be fixed by shortening the delay in the clock line or by increasing the delay in the data path.

What is setup violation and hold violation?If the setup check is violated, data will not be captured properly at the next clock edge. Similarly, if hold check is violated, data intended to get captured at the next edge will get captured at the same edge.

Article first time published onWhy setup time is required?

This duration is known as setup time. The data that was launched at the previous clock edge should be stable at the input at least setup time before the clock edge. So, adherence to setup time ensures that the data launched at previous edge is captured properly at the current edge.

What are setup time and hold time constraints?

The setup time constraint depends on the maximum delay from register R1 through the combinational logic. before the clock edge. The hold time constraint depends on the minimum delay from register R1 through the combinational logic. after the clock edge.

What are clock path timing checks?

It’s very important to understand this clearly to understand and analysing the Timing analysis report and fixing the timing violation. Data path. Start Point. Input port of the design (because the input data can be launched from some external source). Clock pin of the flip-flop/latch/memory (sequential cell)

How do I fix a VLSI hold violation?

- Insert delay elements: This is the simplest we can do, if we are to decrease the magnitude of a hold time violation. …

- Reduce the drive strength of data-path logic gates: Replacing a cell with a similar cell of less drive strength will certainly add delay to data-path.

How do I fix data cap violations in VLSI?

The capacitance on a node is a combination of the fan-out of the output pin and capacitance of the net. This check ensures that the device does not drive more capacitance than the device is characterized for. The violation can be removed by increasing the drive strength of the cell.

Can setup and hold violation on same path?

It is possible to have both setup/hold violations on the same reg2reg path: if you have big “delta delay”, which is due to big coupling capacitance on some nets in the path. During setup analysis, the tool add this “delta delay” to the total path length (so you may have setup violations).

How do you fix the hold time violation after the chip was fabricated?

There is no way to fix setup or hold violation after fabrication. One thing generally industry does is to sell the chip at lower operating frequency if there is setup violation. If there is a hold violation, chip will be thrown into garbage.

Which of the following can be followed in order to fix the setup time violations in VLSI?

Play with clock skew: Positive skew helps improve the setup slack. So, to fix setup violation, we may either choose to increase the clock latency of capturing flip-flop, or decrease the clock latency of launching flip-flop.

Why are violations fixed after CTS?

Clock is propagated only after CTS (actual clock tree is built, clock buffers are added & clock tree hierarchy, clock skew, insertion delay comes into picture) and that’s why hold violations are fixed only after CTS.

Why do we check hold after CTS?

Clock will be propagated only after CTS, till then it will be in Ideal mode i.e delay in the clock path will not be calculated which is optimistic for hold analysis. That is why hold violations will be checked after CTS.

What is negative hold time?

If a circuit has a negative hold time, this means that the input can change before the clock edge and nevertheless the old level will be correctly recognized. This can be produced by internal delay of the clock signal. For example, if a D flip flop has a hold time of –1ns, the level present at the D input.

How is hold slack calculated?

hold slack= Data Arrival Time– Data Required Time A +ve setup slack means design is working at the specified frequency and it has some more margin as well.

Can jitter in clock effect set and hold violations?

clock jitter hold time violation BTW, jitter do affect hold time violation. Jitter is caused by the crosstalk on the clock nets (victim here). In that case, the clock net becomes either slower or faster based on the crosstalk. This impacts the hold timing.

Can setup time be negative?

Negative setup time: When setup time point occurs after clock edge, setup time is said to be negative. Figure 3 shows timing waveform for negative setup time. … Depending upon the relative arrival times of data and clock, setup time can be positive, zero or negative.

What is difference between setup and hold time?

Setup time is the amount of time required for the input to a Flip-Flop to be stable before a clock edge. Hold time is similar to setup time, but it deals with events after a clock edge occurs. Hold time is the minimum amount of time required for the input to a Flip-Flop to be stable after a clock edge.

What is meant by setup time?

What is Setup Time? Setup time is the interval needed to adjust the settings on a machine, so that it is ready to process a job. Shortening the amount of setup time is critical for engaging in short production runs, so that a business can more easily engage in just-in-time production.

What is the difference between a latch and a flip-flop?

Both latches and flip-flops are circuit elements whose output depends not only on the current inputs, but also on previous inputs and outputs. The difference between a latch and a flip-flop is that a latch does not have a clock signal, whereas a flip-flop always does.

What are timing constraints?

Timing constraints is a vital attribute in real-time systems. Timing constraints decides the total correctness of the result sin real-time systems. The correctness of results in real-time system does not depends only on logical correctness but also the result should be obtained within the time constraint.

Why timing analysis is done?

Timing analysis must ensure that any clocks that are generated by the logic are clean, are of bounded period and duty cycle, and of a known phase relationship to other clock signals of interest. The clock must, for both high and low phases, meet the minimum pulse width requirements.

What is the delay of the longest circuit path?

For this circuit, the longest delay path is through the exclusive or gate and the multiplexor. The sum of the propagation delay across these 2 gates is 2.1 + 1.5 = 3.6 ns.